# Charting the future (and remembering the past) of optical lithography simulation

Chris A. Mack<sup>a)</sup>

KLA-Tencor, 1605 Watchhill Road, Austin, Texas 78703

(Received 28 June 2005; accepted 3 October 2005; published 30 November 2005)

Optical lithography modeling began in the early 1970s and represented the first serious attempt to describe lithography not as an art, but as a science. Thirty years later, optical lithography continues to make dramatic advances that enable the profitable continuation of Moore's Law. Most if not all of these advances would not be possible without the use of lithography simulators. This article will review the history of lithography simulation, describing a few of the milestone events and important lithographic advances that simulation enabled. This historical review will end with a characterization of the current state of lithography modeling and its important applications in chip design, process development, and manufacturing today. Finally, a prediction of future advances in simulation capabilities will be made as well as how these advances will help to move the industry forward. © 2005 American Vacuum Society. [DOI: 10.1116/1.2130354]

## I. INTRODUCTION

Optical lithography modeling began in the early 1970s when Rick Dill and his team described the basic steps of the lithography process with mathematical equations. At a time when lithography was considered a true art, such an approach was met with much skepticism. The results of their pioneering work were published in a landmark series of papers in 1975, 1-4 now referred to as the "Dill papers." These papers not only gave birth to the field of lithography modeling, they represented the first serious attempt to describe lithography not as an art, but as a science. These papers presented a simple model for image formation with incoherent illumination, the first order kinetic "Dill model" of exposure, and an empirical model for development coupled with a cell algorithm for photoresist profile calculation. The Dill papers are still among the most referenced works in the body of lithography literature.

Thirty years later, optical lithography continues to make dramatic advances that enable the profitable continuation of Moore's Law. Most if not all of these advances would not be possible without the use of lithography simulators. This article will briefly review the history of lithography simulation, ending with a characterization of the current state of lithography modeling and a prediction of future advances in simulation capabilities.

## II. NEED FOR LITHOGRAPHY SIMULATION

In the early days of semiconductor manufacturing, lithography was widely regarded as an art. The experienced lithographer, practiced in this art through on-the-job training, was able to deliver results but not always able to explain how or why. Processes were optimized (or at least made acceptable) through trial and error. Resolution limits were largely unexplored and feature sizes were many times larger than the wavelength of the light used. Even still, lithography was not

easy and it often limited the successful manufacture of then state-of-the-art devices. Progress was made, but it was obvious that more could be done with a more enlightened approach. As Larry Thompson noted as late as 1983, "...it is of paramount importance that we transform the important area of lithographic processing from an art to a science.<sup>5</sup>"

The transformation of semiconductor lithography from art to science began in the early 1970s, and in my opinion is largely complete today. Mass production at very close to the (now well understood) theoretical limits of a given imaging technology is common. It is likely that 193 nm wavelength imaging will produce sub-100 nm pitch patterns in an amazing extension of optics to its extreme limits. The scientific approach to lithography is responsible for the amazing progress in resolution—beyond anyone's wildest predictions—that continues to enable Moore's Law. And at the very heart of this scientific makeover has been lithography simulation.

## **III. EARLY YEARS**

Optical lithography modeling began in the early 1970s when Rick Dill started an effort at IBM Yorktown Heights Research Center to describe the basic steps of the lithography process with mathematical equations. Rick was frustrated with his ability to predict, or even intuit, the outcome of a lithographic experiment. Having come from a background in device physics where modeling was commonly used, he longed for similar scientific rigor to aid in his lithographic researches.

Dill began by thinking about the modeling problem as simply as possible—in one dimension. Given an open-frame exposure of a photoresist film on an unpatterned wafer, what was the lithographic result as a function of depth into the resist? Dill first broke up the lithographic process into a sequence of needed calculations: the intensity of light inside the resist (a calculation of the standing waves), the chemical concentration of exposure products resulting from this light, the impact of this chemistry on the development rate, and

<sup>&</sup>lt;sup>a)</sup>Electronic mail: chris.a.mack@kla-tencor.com

finally the integration of the development rate through time to predict the resist thickness after development. By noticing that the diazo-type positive resists in use at the time "bleached" (become more transparent) upon exposure, Dill used this change in optical absorbance as a way of monitoring the kinetics of exposure. The key to photoresist development modeling was the creation of a development rate monitor a modified version of the thin film measurement tool IBM was soon to commercialize. By measuring resist thickness in real time during development, development rate could be calculated as a function of depth into the resist. By repeating this measurement for many exposure doses, and using the Dill exposure model to relate incident dose to amount of chemical change within the resist, development rate as a function of the chemical composition of the resist was determined.

The pieces were now all in place. His one-dimensional models accurately predicted the development rate as a function of depth into the resist. By combining these models with a simple incoherent imaging model and Andy Neureuther's cell algorithm for development, the first lithography simulator was created. The results of this pioneering work were published in a landmark series of papers in 1975, <sup>1-4</sup> now referred to as the "Dill papers." These papers not only gave birth to the field of lithography modeling, they represented the first serious attempt to describe lithography not as an art, but as a science.

While Dill's group worked on the beginnings of lithography simulation, a professor from the University of California at Berkeley, Andy Neureuther, spent a year on sabbatical working with Dill. Upon returning to Berkeley, Neureuther and another professor, Bill Oldham, started their own modeling effort. In 1979 they presented the first result of their effort, the lithography modeling program SAMPLE. SAMPLE improved the state of the art in lithography modeling by adding partial coherence to the image calculations, adding a surface inhibition function to the development rate calculation, and replacing the cell algorithm for dissolution calculations with a string algorithm, which gave better results for larger grid sizes. But more importantly, SAMPLE was made available to the lithography community. For the first time, researchers in the field could use modeling as a tool to help understand and improve their lithography processes. By the mid 1980s, simulation had a small but dedicated core following of people that recognized the need for using simulation when faced with the most complex lithography challenges.

#### **IV. PROLITH YEARS**

I began working in the field of lithography in 1983 at the National Security Agency. Inspired by Rick Dill's 1975 papers, I began to work on my own lithography simulation software. After about one year I had finished a very early version of the PC software I called PROLITH, the Positive Resist Optical Lithography model. Building on the work of Dill and Neureuther and their teams, I derived an analytical expression for the standing wave intensity (rather than using the matrix calculation approach that Dill chose) and pro-

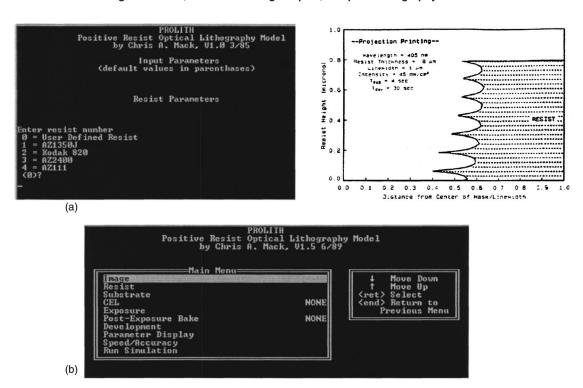

posed a kinetic model for resist dissolution that later came to be called the Mack model. This first simulation effort was published in 1985 after being presented at the SPIE Microlithography Symposium that year. For the next four years, the PROLITH software was updated to include contrast enhancement layers, partially coherent imaging, different approaches for extracting the dimension of a complex resist cross section, and the "high numerical aperture (NA)" effect of image defocus through the thickness of the resist (Fig. 1).

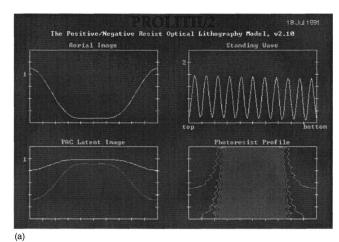

The continued interest and growing importance of PROLITH in the semiconductor industry prompted me to commercialize the software. FINLE Technologies was formed in February, 1990, and the first commercial version of what was now dubbed PROLITH/2 (the second generation of the PROLITH software) was released in June of that year. While still a DOS program, PROLITH began to take advantage of the improving graphics capabilities of the PC, as well as the gradual move towards graphical user interfaces [Fig. 2(a)]. By the end of the decade the inevitable switch to Windows had taken place [Fig. 2(b)].

#### V. IMPACT OF LITHOGRAPHY SIMULATION

In the 30 years since optical lithography modeling was first introduced to the semiconductor industry, it has gone from a research curiosity to an indispensable tool for research, development, and manufacturing. There are numerous examples of how modeling has had a dramatic impact on the evolution of lithography technology, and many more ways in which it has subtly, but undeniably, influenced the daily routines of lithography professionals. There are four major uses for lithography simulation: (1) as a research tool, performing experiments that would be difficult or impossible to do any other way, (2) as a development tool, quickly evaluating options, optimizing processes, or saving time and money by reducing the number of experiments in the fab, (3) as a manufacturing tool, for troubleshooting process problems and determining optimum process settings, and (4) as a learning tool, to help provide a fundamental understanding of all aspects of the lithography process. These four applications of lithography simulation are not distinct—there is much overlap among these basic categories.

# A. Research tool

Since the initial introduction of lithography simulation in 1975, modeling has had a major impact on research efforts in lithography. Here are some early examples of how modeling has been used in research.

After phase-shifting masks were first introduced, modeling has proven to be indispensable in their study. Off-axis illumination was first introduced as a technique for improving resolution and depth of focus based on modeling studies. Since then, this technique has received widespread attention and has been the focus of many more simulation and experimental efforts. Using modeling, the advantages of having a variable numerical aperture, variable partial coherence stepper were first discussed. Since then, all major stepper vendors have offered variable NA, variable coherence systems

FIG. 1. Examples of early user interfaces of PROLITH: (a) v1.0 circa 1985, and (b) v1.5 circa 1989.

and modeling remains a critical tool for optimizing the settings of these flexible machines. Modeling has been used in photoresist studies to understand the depth of focus loss when printing contacts in negative resists, the reason for artificially high values of resist contrast when surface inhibition is present, the potential for exposure optimization to maximize process latitude, and the role of diffusion in chemically amplified resists. Modeling has always been used as a tool for quantifying optical proximity effects and for defining algorithms for optical proximity correction (OPC). Most people would consider modeling to be a required element of any OPC scheme. Defect printability has always been a difficult problem to understand. Modeling has been used to study the printability of defects dependant on the imaging system and resist used, as well as the position of the defect relative to other patterns on the mask and the size and transmission properties of the defect. Modeling has proven an indispensable tool for predicting future lithographic performance and evaluating the theoretical capabilities and limitations of extensions for optical lithography far into the future.

One of the primary reasons that lithography modeling has become such a standard tool for research activities is the ability to simulate such a wide range of lithographic conditions. While laboratory experiments are limited to the equipment and materials on hand (a particular wavelength and numerical aperture of the stepper, a given photoresist or film stack), simulation gives an almost infinite array of possible conditions. From high numerical apertures to low wavelengths, hypothetical resists to arbitrary mask structures, simulation offers the ability to run "experiments" on steppers

that do not exist with photoresists that have yet to be made. How else can one explore the shadowy boundary between the possible and the impossible?

#### B. Process development tool

Lithography modeling has also proven to be an invaluable tool for the development of new lithographic processes or equipment. Some of the more common uses include the optimization of optical properties of photoresists, simulation of substrate reflectivity, and the applicability and optimization of top and bottom antireflection coatings. In addition, simulation has been used to help understand the use of thick resists for thin film head manufacture as well as other nonsemiconductor applications. Modeling is used extensively by makers of photoresist to evaluate new formulations and to determine adequate measures of photoresist performance for quality control purposes. Resist users often employ modeling as an aid for new resist evaluations. On the exposure tool side, modeling has become an indispensable part of the optimization of the numerical aperture and illumination conditions of a stepper and in the understanding of the impact of aberrations. The use of optical proximity correction software requires rules on how to perform the corrections, which are often generated with the help of lithography simulation, or they use lithography models directly for the corrections.

As a development tool, lithography simulation excels due to its speed and cost effectiveness. Process development usually involves running numerous experiments to determine optimum process conditions, shake out possible problems, determine sensitivity to variables, and write specification

FIG. 2. Examples of the user interfaces of the commercial version of PRO-LITH: (a) the DOS version 2.1, circa 1991, and (b) the Windows version 6.0, circa 1999.

limits on the inputs and outputs of the process. These activities tend to be both time consuming and costly. Modeling offers a way to supplement laboratory experiments with simulation experiments to speed up this process and reduce costs. Considering that a single experimental run in a wafer fabrication facility can take from hours to days, the speed advantage of simulation is considerable. This allows a greater number of simulations than would be practical (or even possible) in the fab.

## C. Manufacturing tool

The use of simulation in a manufacturing environment has three primary goals: to reduce the number of test or experimental wafers which must be run through the production line, to troubleshoot problems in the fab, and to aid in decision making by providing facts to support engineering judgment and intuition. Running test wafers through a manufacturing line is costly not so much due to the cost of the test, but due to the opportunity cost of not running product. If simulation can reduce the time a manufacturing line is not running product even slightly, the return on investment can be significant. Simulation can also aid in the time required to bring a new process on-line and in the establishment of the

base-line capability of a new process. Although not a complete list, the most common use cases for lithography simulation in a manufacturing environment are:

- Film Stack Optimization

- Process Window Prediction

- NA/ $\sigma$  optimization

- OPC Verification

- CD Limited Yield, Cpk Analysis

- Troubleshooting/Root Cause Analysis

## D. Learning tool

Although the research, development, and manufacturing applications of lithography simulation presented above give ample benefits of modeling based on time, cost, and capability, the underlying power of simulation is its ability to act as a learning tool. Proper application of modeling allows the user to learn efficiently and effectively. There are many reasons why this is true. First, the speed of simulation versus experimentation makes feedback much more timely. Since learning is a cycle (an idea, an experiment, a measurement, then comparison back to the original idea), faster feedback allows for more cycles of learning. Since simulation is very inexpensive, there are fewer inhibitions and more opportunities to explore ideas. And, as the research application has shown us, there are fewer physical constraints on what "experiments" can be performed. In addition, simulation allows one to "see" intermediate parts of the imaging sequence, like aerial images, latent images, and substrate reflectivity, that are not observable in practice. All of these factors allow the use of modeling to gain an understanding of lithography. Whether learning fundamental concepts or exploring subtle nuances, the value of improved knowledge cannot be overstated.

The list above is, by necessity, extremely incomplete. It is also quite dated. While it was easy in the early years of the history of simulation to identify milestone papers that illustrated the importance of simulation to the four use cases described above, today it is much more difficult. Simulation is so well ingrained into the working world of the lithographer today that it is difficult to single out any small handful of papers as being significant above the rest in their use of simulation.

## VI. FUTURE OF LITHOGRAPHY SIMULATION

Lithography simulation has for 30 years served two essential purposes: to validate and improve the industry's theoretical understanding of lithography, and to provide a tool to the average lithographer to apply this theory to real lithography problems. By both of these measures, the industry's efforts in lithography simulation have been extremely successful. It is not an overstatement to say that semiconductor manufacturing as we know it today would not be possible without lithography simulation.

But just as lithography technology moves at a harried pace toward finer features, simulation technology must move just as fast to stay with, or ahead of, the needs of lithography

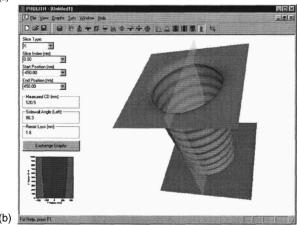

Fig. 3. Example of breaking up a simulation domain into mesoscale "cells."

technology development. The future of simulation will be even more challenging than the past has been—but success is a requirement. There are three major areas of lithography simulation development for the foreseeable future: improved accuracy, improved simulation speed, and the addition of new physical phenomena.

## A. Accuracy

Lithographers want simulation to be more accurate than their experimental data. While this goal may seem unattainable, in fact it is quite possible. Borrowing the ideas and terminology of metrology tools, the goal is to keep the total simulation uncertainty below the total measurement uncertainty of a critical dimension measurement. For example, a requirement for a lithography simulator might be a total simulation uncertainty of less than 2 nm at the 65 nm node. Much, probably most, of the focus of model and simulator development today is on achieving greater accuracy.

Like metrology data, simulation uncertainty can be broken down into two components: precision and accuracy. Precision is the result of numerical errors in solving the model equations. Like a metrology tool, the precision to tolerance ratio of a simulator should be less than 0.2 (and ideally should be as low as 0.1). This means that simulator precision should be less than  $\pm 2\%$  of the target CD. Of course, simulation precision is not a random error, so precision specifications for a simulator are based on maximum numerical errors over the widest possible range of input parameters. Accuracy is a consequence of the goodness of the models themselves,

and how well those models have been calibrated to a given process. In general, calibration is the primary limiter of accuracy for the high accuracy physically based simulators of today. In order to meet the seemingly unrealistic goal of simulating features with greater accuracy than they can be measured, very careful measurement of all input parameters is needed. In addition, comparison of simulation results to metrology results (where a fraction of a nanometer is significant) is not possible without a careful understanding of the physics and algorithms of the metrology tool.

## B. Speed

Simulator speed is important whenever the usefulness of the results is limited by how long one must wait to get the answers. While improvements in simulator speed are always welcome, dramatic improvements can in fact enable dramatic new applications. For example, what if high accuracy simulations, currently available over simulation areas of just tens of square microns, could be run for a full chip?

Today, full chip lithographic simulation using approximate image models and empirical resist models has enabled useful optical proximity correction (OPC) technology. These models, however, show reduced accuracy compared to full physical models (3X-10X) less accuracy) over a much narrower range of process conditions as the price paid for sufficient speed to make a full chip simulation practical. There is, then, a need for even faster simulations with more physically based models that provide much better accuracy over a wider range of process conditions for a single calibration.

The present approach to OPC verification has evolved from a number of separate inspection strategies. OPC decoration is verified by a design rule or optical rule checker, the reticle is verified by a reticle inspection system, and the final wafers are verified by wafer inspection and metrology tools. Each verification step looks at a different representation of the desired device pattern with little or no data flowing between them. Although each component is a valuable part of the whole, the desired outcome is to find design-formanufacturing issues as early as possible as this results in the largest savings of resources and money. For example, a defect found before the reticle is made might be corrected in a few days time at a cost of thousands of dollars while a defect found during wafer manufacture could easily cost ten or 100 times as much with a similar increase in lost time. Lithography simulation has great potential in connecting the data between each of these verification steps and enabling full chip verification across the entire lithography process window at an early stage-optimizing the design for the actual manufacturing process.

To accomplish this, a simulation system would need to model how the design will be transferred to the reticle layer and how that reticle will be imaged into resist across the full focus-exposure process window. Simulated images could be compared to the desired pattern, and defect detection algorithms could then be applied to determine if any unacceptable variations in the pattern occur within the nominal process window. Recently, a simulation system designed to

address such a need was described. By combining vector image calculations with a new resist model and specialized supercomputing hardware, a full chip (8 mm square on the wafer) can be simulated through 35 focus and exposure points in 2 h. The  $3\sigma$  matching of simulator results to experimental CDs through size and pitch over a range of focus and exposure corresponding to the full process window was found to be better than  $\pm 5$  nm.

## C. Physics

An interesting effort at several universities (the University of Texas at Austin being predominate) involves so-called mesoscale modeling, working down closer to the molecular level for its physical descriptions. <sup>10,11</sup> As illustrated in Fig. 3, the simulation domain is broken down into several mesoscale (medium sized) cells, roughly 0.7 nm square, each containing an important subcomponent of the resist (an acid molecule, a region of free volume, a blocked polymer site, etc.). Using Monte Carlo techniques, movements and reactions of the components are followed through time to predict lithographic results. While much work remains to be done, mesoscale modeling efforts could one day aid in resist design and provide invaluable insight into the mechanisms of line-edge roughness formation and statistical feature size fluctuations.

The remarkable successes of lithography simulation reflect the broader successes of lithography technology development and semiconductor manufacturing advancement. And just as the continued improvements in resolution and manufacturability in our industry seem inevitable, so too will lithography simulation development continue and advance.

<sup>1</sup>F. H. Dill, IEEE Trans. Electron Devices **ED-22**, 440 (1975).

<sup>2</sup>F. H. Dill, W. P. Hornberger, P. S. Hauge, and J. M. Shaw, IEEE Trans. Electron Devices **ED-22**, 445 (1975).

<sup>3</sup>K. L. Konnerth and F. H. Dill, IEEE Trans. Electron Devices **ED-22**, 452 (1975)

<sup>4</sup>F. H. Dill, A. R. Neureuther, J. A. Tuttle, and E. J. Walker, IEEE Trans. Electron Devices **ED-22**, 456 (1975).

<sup>5</sup>Introduction to Microlithography, edited by L. F. Thompson, C. G. Willson, and M. J. Bowden, ACS Symposium Series, No. 219 (1983).

<sup>6</sup>For a more complete history of this effort, see Rick Dill's paper "The Basis for Lithographic Modeling" Proc. SPIE **5754** (2005).

<sup>7</sup>W. G. Oldham, S. N. Nandgaonkar, A. R. Neureuther, and M. O'Toole, IEEE Trans. Electron Devices **ED-26**, 717 (1979).

<sup>8</sup>C. A. Mack, Proc. SPIE **538**, 207 (1985).

<sup>9</sup>W. Howard, J. Tirapu, A. Y. Xiong, C. Mack, G. Verma, W. Volk, H. Lehon, Y. Deng, R.-F. Shi, J. Culp, and S. Mansfield, Proc. SPIE 5756, 61 (2005).

<sup>10</sup>G. M. Schmid, M. D. Stewart, S. D. Burns, and C. G. Willson, J. Electrochem. Soc. **151**, G155 (2004).

<sup>11</sup>J. E. Meiring, T. B. Michaelson, A. T. Jamieson, G. M. Schmid, and C. G. Willson, Proc. SPIE 5753, 350 (2005).